Servizzi ta' Manifattura Elettronika one-stop, jgħinuk tikseb faċilment il-prodotti elettroniċi tiegħek minn PCB & PCBA

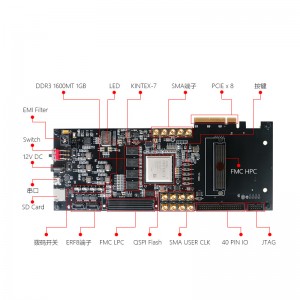

Komunikazzjoni tal-fibra ottika FPGA Xilinx K7 Kintex7 PCIe

- DDR3 SDRAM: 16GB DDR3 64bit bus, rata tad-dejta 1600Mbps

- QSPI Flash: Biċċa QSPIFLASH ta' 128mbit, li tista' tintuża għal fajls ta' konfigurazzjoni FPGA u ħażna ta' dejta tal-utent

- Interfaċċja PCLEX8: L-interfaċċja standard PCLEX8 tintuża biex tikkomunika mal-komunikazzjoni PCIE tal-motherboard tal-kompjuter. Tappoġġja l-istandard PCI, Express 2.0. Ir-rata ta' komunikazzjoni b'kanal wieħed tista' tkun għolja sa 5Gbps

- Port serjali USB UART: Port serjali, qabbad mal-PC permezz tal-kejbil miniusb biex twettaq komunikazzjoni serjali

- Karta Micro SD: Is-sedil tal-karta Microsd kollu kemm hu, tista' tqabbad il-karta Microsd standard

- Senser tat-temperatura: ċippa tas-sensur tat-temperatura LM75, li tista' tissorvelja t-temperatura ambjentali madwar il-bord tal-iżvilupp

- Port ta' estensjoni FMC: FMC HPC u FMCLPC, li jistgħu jkunu kompatibbli ma' diversi karti ta' bord ta' espansjoni standard

- Terminal ta' konnessjoni b'veloċità għolja ERF8: 2 portijiet ERF8, li jappoġġjaw trasmissjoni ta' sinjali b'veloċità ultra-għolja. Estensjoni ta' 40pin: riżervata interface IO ta' estensjoni ġenerali b'2.54mm40pin, O effettiva għandha 17-il par, jappoġġjaw 3.3V.

- Il-konnessjoni periferali tal-livell u l-livell ta' 5V tista' tgħaqqad il-periferali periferali ta' interfejsijiet 1O ta' skop ġenerali differenti

- Terminal SMA; 13-il ras SMA indurati bid-deheb ta' kwalità għolja, li huwa konvenjenti għall-utenti biex jikkooperaw ma' karti ta' espansjoni AD/DA FMC ta' veloċità għolja għall-ġbir u l-ipproċessar tas-sinjali

- Ġestjoni tal-Arloġġ: Sors ta' arloġġi multipli. Dawn jinkludu s-sors tal-arloġġ differenzjali tas-sistema ta' 200MHz SIT9102

- Oxxillazzjoni tal-kristall differenzjali: kristall ta' 50MHz u ċippa tal-ġestjoni tal-arloġġ programmabbli SI5338P: mgħammra wkoll b'

- 66MHz EMCCLK. Jista' jadatta b'mod preċiż għal frekwenzi differenti tal-arloġġ tal-użu

- Port JTAG: 10 ponti Port JTAG standard ta' 2.54mm, għat-tniżżil u d-debugging tal-programmi FPGA

- Ċippa ta' monitoraġġ tal-vultaġġ sub-reset: biċċa ċippa ta' monitoraġġ tal-vultaġġ ADM706R, u l-buttuna bil-buttuna tipprovdi sinjal ta' reset globali għas-sistema

- LED: 11-il dwal LED, jindikaw il-provvista tal-enerġija tal-karta tal-bord, sinjal config_done, FMC

- Sinjal indikatur tal-enerġija, u 4 LEDs tal-utent

- Ċavetta u swiċċ: 6 ċwievet u 4 swiċċijiet huma buttuni ta' reset tal-FPGA,

- Il-buttuna tal-Programm B u 4 ċwievet tal-utent huma komposti. 4 swiċċijiet b'żewġ tarmi b'sikkina waħda

Ikteb il-messaġġ tiegħek hawn u ibgħatu lilna

Kategoriji ta' prodotti

-

Telefon

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype